在人工智能技術飛速發展的今天,大模型以其強大的通用能力和涌現特性,成為推動產業智能化變革的核心引擎。如何讓這些“聰明”的模型真正走出實驗室,在千行百業中創造實際價值,是當前業界面臨的關鍵挑戰。對此,資深技術專家云段永華明確指出:大模型的應用落地,絕不能脫離具體場景空談技術,必須深度結合業務場景進行探索與創新,這同樣是驅動新一代人工智能應用軟件開發模式轉型的根本路徑。

云段永華的觀點深刻揭示了當前大模型產業化進程中的核心矛盾:技術潛力巨大與落地成效不足并存。許多企業和開發者往往陷入對模型參數規模、榜單分數的盲目追求,卻忽略了最根本的問題——這項技術究竟要解決什么具體業務問題?在哪個環節、為誰創造價值?他指出,大模型的優勢在于其強大的理解、生成、推理和泛化能力,但這些能力是“原材料”,而非“最終產品”。如同優質的鋼材,必須經過精密的加工和設計,才能變成特定場景下耐用的器械。

因此,“結合場景去探索” 成為大模型落地的第一性原則。這要求開發者和企業必須完成從“技術導向”到“場景驅動”的思維轉變。具體而言,首先需要進行深度的場景解構與分析:識別業務流中的痛點、高頻交互環節、知識密集領域以及價值創造節點。例如,在金融領域,可能是智能投研報告生成、合規審查與風險預警;在醫療領域,可能是輔助診斷報告解讀、病歷信息結構化與科研文獻分析;在客服領域,則是個性化交互、多輪對話與復雜問題排查。每個場景都有其獨特的數據特征、專業知識、流程約束和價值衡量標準。

基于精準的場景洞察,人工智能應用軟件的開發范式也隨之革新。云段永華認為,傳統的軟件開發流程,如需求分析、設計、編碼、測試,在面對大模型這種非確定性、持續演化的“新組件”時,需要引入更敏捷、更注重反饋與迭代的“場景化工程”方法。這包括:

- 場景化數據工程與精調:針對特定場景收集、清洗、標注高質量數據,并利用這些數據對大模型進行領域適應性的微調(Fine-tuning)或提示工程(Prompt Engineering),使其輸出更專業、更可控、更符合業務規范。

- 混合智能系統設計:大模型并非萬能。在關鍵決策、高可靠性要求的場景中,需要設計“大模型+規則引擎”、“大模型+傳統算法”、“大模型+人類審核”的混合架構,將大模型的創造力與規則的確定性、人類的判斷力相結合,構建安全、可靠、可信的應用系統。

- 場景化評估與持續優化:建立與業務指標強關聯的評估體系,不僅評估模型的通用能力,更要評估其在具體場景下的任務完成度、準確性、效率提升和用戶體驗。通過持續的場景反饋數據,對模型和應用進行迭代優化,形成“場景驅動優化”的閉環。

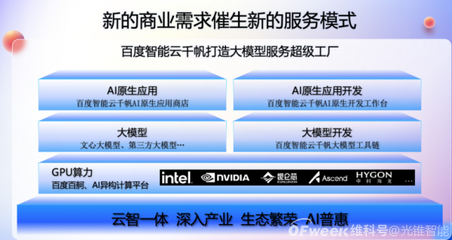

- 低門檻與工具鏈支持:為了讓更多領域的專家能夠參與到大模型的應用構建中,需要開發面向場景的低代碼/無代碼工具、領域特定的提示詞模板庫、以及易于集成的API服務,降低人工智能應用軟件開發的技術壁壘。

總而言之,云段永華的見解為人工智能應用軟件的未來發展指明了方向。大模型的落地不是簡單的技術集成,而是一場深刻的、以場景為中心的創新實踐。它要求開發者具備跨界的理解力,既能洞悉技術邊界,又能深耕行業知識。只有將大模型的能力錨定在真實、具體、有價值的業務場景中,通過場景化的工程方法將其轉化為穩定、可靠、易用的軟件功能,才能真正釋放人工智能的普惠價值,推動各行各業的智能化升級,書寫人工智能應用軟件開發的新篇章。