在西安這座古老與現代交融的城市,曲江新區正以其蓬勃的創新活力,成為數字經濟發展的熱土。這里,一群智慧的實踐者——超數智慧團隊,正以信息電子技術服務為基石,深耕大數據領域,用技術與創新詮釋著新時代的奮斗精神。

一、時代浪潮:擁抱大數據,定義新服務

我們正處于一個數據驅動變革的時代。大數據不再是抽象的概念,而是滲透到城市管理、產業升級、民生服務各個領域的核心生產要素。超數智慧團隊敏銳地捕捉到這一趨勢,將自身定位為“智慧實踐者”。他們不僅僅是技術的提供者,更是深入行業場景,將復雜的數據流轉化為清晰洞察和高效決策方案的賦能者。其核心業務——信息電子技術服務,涵蓋了從數據采集、存儲、處理、分析到可視化應用的全鏈條,為政府、企業構建起堅實的數字化底座。

二、曲江舞臺:創新沃土上的智慧深耕

曲江新區濃厚的文化底蘊與對科技創新的鼓勵政策,為超數智慧提供了絕佳的發展舞臺。在這里,團隊將大數據技術與區域特色相結合。例如,在文化旅游領域,通過分析游客流量、消費偏好等數據,助力景區實現智慧化管理與個性化服務推薦;在城市治理方面,利用物聯網傳感器數據優化交通調度、環境監測,讓城市運行更“聰明”。他們的奮斗,是扎根于具體場景,解決實際問題的務實創新,讓數據智慧在曲江這片土地上生根發芽,開花結果。

三、實踐之路:從技術到價值,賦能千行百業

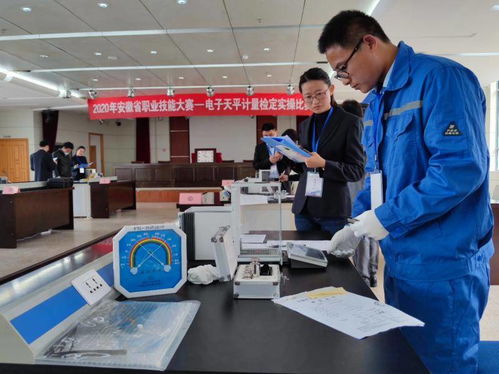

作為“智慧實踐者”,超數智慧的核心能力在于將前沿技術轉化為客戶價值。團隊深諳,大數據服務的終點不是報表和圖表,而是可感知的效率提升與模式創新。在智能制造領域,通過設備運行數據分析,實現預測性維護,降低停機風險;在金融服務中,利用風控模型精準評估信用,提升服務安全與效率;在電子政務服務中,打通數據壁壘,讓“數據跑路”替代“群眾跑腿”。每一次成功的項目落地,都是對“信息電子技術服務”內涵的深化,也是對“奮斗”一詞最生動的注解——用持續的技術迭代與貼心的服務,陪伴客戶共同成長。

四、未來展望:持續奮斗,共繪智慧新藍圖

隨著人工智能、物聯網與大數據融合的不斷深入,智慧化應用將擁有更廣闊的想象空間。奮斗在曲江的超數智慧團隊,將繼續秉持實踐者的初心,不斷探索數據潛能。他們的目標不僅是成為優秀的技術服務商,更希望成為各行各業數字化轉型進程中可靠的伙伴,共同推動社會向著更加智能、高效、便捷的方向發展。

在曲江,奮斗是創新的代碼,智慧是實踐的果實。超數智慧團隊,這群大數據時代的弄潮兒,正以信息電子技術為筆,以海量數據為墨,在時代的畫卷上,奮力書寫著屬于智慧實踐者的精彩篇章。他們的故事證明,真正的智慧,源于對技術的深刻理解,更源于對服務價值的執著追求與不懈奮斗。